# Two-temperature principle for evaluating electrothermal performance of GaN HEMTs

Cite as: Appl. Phys. Lett. **124**, 042107 (2024); doi: 10.1063/5.0189262 Submitted: 28 November 2023 · Accepted: 8 January 2024 · Published Online: 24 January 2024

Yang Shen 🕞 and Bingyang Cao<sup>a)</sup> 🕞

## **AFFILIATIONS**

Key Laboratory of Thermal Science and Power Engineering of Education of Ministry, Department of Engineering Mechanics, Tsinghua University, Beijing 100084, China

Note: This paper is part of the APL Special Collection on Advances in Thermal Phonon Engineering and Thermal Management.

a) Author to whom correspondence should be addressed: caoby@tsinghua.edu.cn

# **ABSTRACT**

Self-heating effects in Gallium nitride (GaN) high-electron-mobility transistors (HEMTs) can adversely impact both device reliability and electrical performance. Despite this, a holistic understanding of the relationship among heat transport mechanisms, device reliability, and degradation of electrical performance has yet to be established. This Letter presents an in-depth analysis of self-heating effects in GaN HEMTs using technology computer-aided design and phonon Monte Carlo simulations. We examine the differential behaviors of the maximum channel temperature ( $T_{\rm max}$ ) and the equivalent channel temperature ( $T_{\rm eq}$ ) in response to non-Fourier heat spreading processes, highlighting their respective dependencies on bias conditions and phonon ballistic effects. Our study reveals that  $T_{\rm max}$ , a crucial metric for device reliability, is highly sensitive to both heat source-related and cross-plane ballistic effects, especially in the saturation regime. In contrast,  $T_{\rm eq}$ , which correlates with drain current degradation, shows minimal bias dependence and is predominantly influenced by the cross-plane ballistic effect. These findings emphasize the importance of optimizing device designs to mitigate both  $T_{\rm max}$  and  $T_{\rm eq}$ , with a particular focus on thermal designs influenced by the heat source size. This work contributes to a deeper understanding of self-heating phenomena in GaN HEMTs and provides valuable insights for enhancing device performance and reliability.

Published under an exclusive license by AIP Publishing. https://doi.org/10.1063/5.0189262

Gallium nitride (GaN) high-electron-mobility transistors (HEMTs) have emerged as prominent components in high-frequency and high-power applications due to their exceptional electronic properties. Despite these advantages, a significant challenge associated with GaN HEMTs is device overheating. This overheating threatens both the reliability and electrical performance of these devices, leading to increased focus on near-junction thermal management and electrothermal co-design, whereas current thermal analysis practices often rely on the maximum channel temperature ( $T_{\rm max}$ ) as the primary metric for estimating device thermal performance. However, recent studies have demonstrated that  $T_{\rm max}$  may not directly correlate with the electrical performance degradation in GaN HEMTs. Instead, Chen *et al.* propose the concept of an equivalent channel temperature ( $T_{\rm eq}$ ) to better quantify such degradation.

Nevertheless, these works use Fourier's law of heat conduction as the basis, which does not capture the complexity of thermal transport processes in GaN HEMTs. Given that the dimensions of the heat source and the GaN layer in these devices are comparable to the mean free paths (MFPs) of phonons, which are the primary heat carriers in semiconductors, Fourier's law becomes inapplicable. In such

scenarios, the non-Fourier effects significantly affect the temperature field within the device and lead to elevated channel temperatures.  $^{12-15}$  Our previous work has quantitatively demonstrated the influence of bias-dependent heat generation and phonon ballistic transport on the temperature distribution in GaN HEMTs.  $^{16}$  We have proposed a two-thermal-conductivity model  $^{16}$  to characterize the bias-dependent  $T_{\rm max}$  based on the two-heat-source model.  $^{17}$  However, the impact of phonon ballistic transport-induced temperature fields on device drain current degradation has not been thoroughly investigated. Therefore, a more comprehensive electrothermal examination that considers electrical transport and phonon thermal transport simultaneously is crucial for accurately evaluating both  $(T_{\rm max})$  and  $(T_{\rm eq})$ , and for developing effective thermal management strategies to enhance device reliability and mitigate electrical performance degradation.

In this study, we employ electrothermal technology computer-aided design (TCAD) simulations, combined with phonon Monte Carlo (MC) simulations, to investigate self-heating effects in GaN HEMTs. Our analysis delves into the bias-dependent heat generation and phonon ballistic transport, examining their impacts on both the  $T_{\rm max}$  and  $T_{\rm eq}$ . Furthermore, we elucidate the mechanisms underlying

these impacts and explain the intricate interplay between non-Fourier heat spreading, device reliability, and the degradation of drain current due to self-heating. This work aims to deepen the understanding of self-heating phenomena and enhance near-junction thermal management strategies in GaN HEMTs.

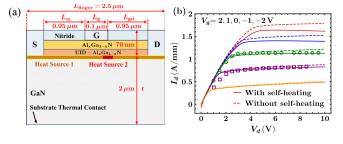

The HEMT structure examined is illustrated in Fig. 1(a), based on the design detailed in Ref. 18. The device comprises five layers, arranged from top to bottom as follows: a SiN passivation layer, an  $Al_xGa_{1-x}N$  barrier layer (with x = 0.25 and donor concentration  $N_d=2\times 10^{18}~{\rm cm}^{-3}$ ), an unintentionally doped (UID) AlGaN spacer layer ( $N_d=1\times 10^{15}~{\rm cm}^3$ ), a GaN buffer layer, and a SiC substrate that functions as a thermal contact. The respective thicknesses of these layers are 50 nm, 18 nm, 2 nm, 1  $\mu$ m, and 10 nm. The gate length ( $L_{\rm g}$ ) of the HEMT is 100 nm, with source and drain access regions each extending 0.95  $\mu$ m ( $L_{\rm sg}=L_{\rm gd}$ ). The device modeling and simulation are carried out using Sentaurus TCAD. The Fourier's law-based thermal equation is solved to account for self-heating effects in TCAD simulations. The thermal boundary conditions include a substrate temperature fixed at 300 K, a thermal boundary resistance of  $1 \times 10^{-8}$  m<sup>2</sup> K/W, and periodic side boundaries. Various heat generation mechanisms are considered, including Joule heat, recombination heat, Thompson heat, and Peltier heat. Electron transport employs the classic drift-diffusion model (DDM), as velocity overshoot is minimally impactful in short gate length GaN HEMTs at modest drain biases, 19 with small discrepancy in heat source distributions compared to predictions by electron Monte Carlo methods. 20 Nonetheless, future work should comprehensively investigate non-local electron transport's effect on heat generation across diverse geometries and biases. The Masetti model is adopted to account for doping dependence of electron mobility,<sup>21</sup> and the Canali model is used to cover temperature and electric field dependence.<sup>22</sup> Figure 1(b) presents the simulated output characteristics of the HEMT. In the current simulation, the GaN layer adopts a thickness-dependent thermal conductivity, set at 120 W/m K. This simulation setup, particularly the model incorporating self-heating effects, demonstrates good agreement with the experimental DC results reported in Ref. 18.

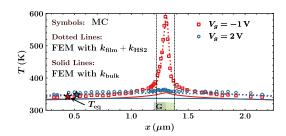

To elucidate the impact of phonon ballistic effects on temperature distribution, we integrate the heat generation profiles obtained from TCAD simulations with phonon Monte Carlo (MC) simulations and finite element method (FEM) analyses. <sup>16,23,24</sup> The specifics of these simulations and the phonon properties utilized are detailed in Ref. 16. Figure 2 depicts the channel temperature profiles as forecasted by MC simulations and FEM under various biases while maintaining a

**FIG. 1.** (a) Schematic of the GaN HEMT. (b) Output characteristics of the HEMT extracted from TCAD simulations with GaN film thermal conductivity of 120 W/m K (lines) and experimental results (symbols). <sup>18</sup>

**FIG. 2.** Channel temperature profiles predicted by MC simulations (symbols), and FEM with  $k_{\rm bulk}$  and  $k_{\rm film}+k_{\rm HS2}$  at different biases with  $P_{\rm diss}=5$  W/mm. The biasing points are ( $V_g$ ,  $V_d$ ) = (-1 V, 6.7 V) and (2 V, 3.8 V). The positions of the gate and the high-field region are marked in the figure.

consistent power dissipation ( $P_{\text{diss}} = 5 \text{ W/mm}$ ). Notably, MC simulations consistently predict higher temperatures across the channel compared to FEM using bulk thermal conductivity ( $k_{\text{bulk}}$ ). This discrepancy is primarily due to two kinds of phonon ballistic effects. The cross-plane ballistic effect, stemming from phonon-boundary scattering, is influenced by the GaN layer's thickness and tends to uniformly raise channel temperatures.<sup>25,26</sup> In contrast, the ballistic effect with the heat source size comparable to MFP primarily elevates the temperature at the heat source. 12,16 Chen et al. observed that under linear operating conditions (drain-to-source voltage  $V_d$  less than saturation voltage V<sub>dsat</sub>), heat dissipates uniformly across the transistor's finger (Heat Source 1, HS1). However, for  $V_d > V_{\text{dsat}}$ , while HS1's heat dissipation peaks, additional heat generation occurs at the drainside gate edge, forming a narrower Heat Source 2 (HS2) region. 16,17 They empirically approximated HS2 to be centered at the drain-side gate edge with a fixed length of  $L_{\rm HS2} = 160$  nm, and the approximation has been validated to be nearly independent of device geometries and biases.

Although solving the phonon Boltzmann transport equation (BTE) and electron transport equations self-consistently offers the most accurate depiction of electron-phonon interactions, this approach is often too time-consuming for extensive quantitative analyses due to its high computational demands.<sup>23</sup> As a compromise for rapid electrothermal co-analysis, we introduce two effective thermal conductivities. The cross-plane effective thermal conductivity ( $k_{\text{film}}$ , set at 120 W/m K) accounts for the cross-plane ballistic effect. Meanwhile, a reduced thermal conductivity ( $k_{HS2} = 8 \text{ W/m K}$ ) is assigned to the HS2 region to reflect the impact of the heat source-induced ballistic effect. As shown in Fig. 2, FEM predictions using  $k_{\text{film}}$  and  $k_{\text{HS2}}$  closely align with MC simulation results across different biases. It is noteworthy that the high-field region's width remains relatively constant across varying bias conditions and device geometries, indicating that the current settings are robust for different scenarios. 16,17 By utilizing these effective thermal conductivities within TCAD simulations to ensure that the resulting temperature distributions are consistent with the MC-predicted profiles, we can investigate the interaction between thermal metrics, the bias dependence of heat generation, and the influence of phonon ballistic transport.

Figure 2 presents  $T_{\rm max}$  and identifies the locations corresponding to the equivalent temperature  $T_{\rm eq}$  under various bias conditions.  $T_{\rm eq}$  is defined as the uniform temperature  $(T_{\rm uniform})$  at which a device is immersed and exhibits a drain current matching that under simulated self-heating conditions, as described by the following equation:

$$T_{\rm eq}(V_g,V_d) = T_{\rm uniform}(V_g,V_d)|_{@I_{d,\rm self-heating} = I_{d,\rm uniform}}. \tag{1}$$

Interestingly, the values and positions of  $T_{\rm eq}$  are nearly consistent across different scenarios, typically situated away from the hotspot region. This indicates that while phonon ballistic transport induced by the heat source markedly increases  $T_{\rm max}$ , its influence on the device's electrical performance is relatively limited.

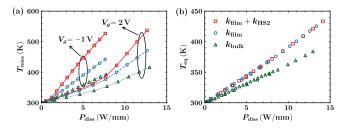

To investigate the relationship between bias dependence, phonon ballistic effects, and the temperature metrics, we perform three parallel TCAD simulations using  $k_{\text{bulk}}$ ,  $k_{\text{film}}$ , and a combination of  $k_{\rm film} + k_{\rm HS2}$ . Figure 3 shows the variations in  $T_{\rm max}$  and  $T_{\rm eq}$  against  $P_{\rm diss}$ for gate voltages of -1 and 2 V, under different thermal conductivity scenarios. In Fig. 3(a),  $T_{\text{max}}$  demonstrates strong bias dependency, with each curve distinctly dividing into linear and saturation regimes at  $V_{\rm dsat}$ . Notably, at  $P_{\rm diss} = 7.5 \, {\rm W/mm}$ , even with  $k_{\rm bulk}$ , the temperature difference between −1 and 2 V gate biases approaches 50 K. Substituting  $k_{\text{bulk}}$  with  $k_{\text{film}}$  to include cross-plane ballistic effects consistently elevates  $T_{\rm max}$  across both regimes. Additionally, incorporating k<sub>HS2</sub> leads to a slight increase in the linear regime compared to using  $k_{

m film}$  alone. However, beyond  $V_d > V_{

m dsat}$ , both  $T_{

m max}$  and its bias dependence significantly increase due to the heat source-related ballistic effect, widening the discrepancy to approximately 100 K. In contrast, Fig. 3(b) indicates that  $T_{\rm eq}$  remains substantially lower than  $T_{\rm max}$  for equivalent  $P_{\rm diss}$  and shows minimal bias dependence. The  $T_{\rm eq}$  results for scenarios with  $k_{\rm film}$  and  $k_{\rm film}+k_{\rm HS2}$  are closely aligned and higher than those using  $k_{\rm bulk}$  alone. This suggests that the self-heatinginduced electrical performance degradation in devices is primarily influenced by the cross-plane ballistic effect. The localized high temperatures at the drain-side gate edge, resulting from concentrated heat generation and quasi-ballistic phonon transport, have a minor impact on the degradation of the device's drain current.

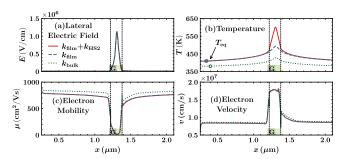

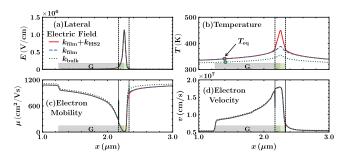

Figures 4(a)–4(d) demonstrate the TCAD-predicted distributions of lateral electric field, temperature, electron mobility, and electron velocity in the channel for varying thermal conductivity settings, elucidating the distinct behaviors of  $T_{\rm max}$  and  $T_{\rm eq}$ . While the electric field distributions are consistent across all scenarios, employing  $k_{\rm film}$ , a common choice in device thermal simulations, results in a uniform temperature increase across the channel compared to using  $k_{\rm bulk}$ . Consequently, electron mobility and velocity in the access regions are adversely affected by the heightened temperatures. In scenarios incorporating  $k_{\rm film} + k_{\rm HS2}$ , the temperature in the HS2 region is specifically elevated due to the heat source-related ballistic effect, while temperatures in other channel regions mirror those observed with  $k_{\rm film}$  alone. Despite these temperature variances in the HS2 region, the distributions of electron mobility and velocity within the channel are nearly

**FIG. 3.** (a)  $T_{\rm max}$  and (b)  $T_{\rm eq}$  varying with  $P_{\rm diss}$  under two biases for various thermal conductivity settings.

**FIG. 4.** Distributions of (a) lateral electric field, (b) temperature, (c) electron mobility, and (d) electron velocity along the HEMT channel with different thermal conductivity settings at  $V_q = 0$ V and  $V_d = 10$  V.

unchanged. This stability is attributed to the concurrent influence of electric field and temperature on these parameters. At lower fields, phonon scattering dominates electron mobility, leading to a noticeable decline as temperature increases. Conversely, at high fields, the electron velocity reaches its saturation value ( $v_{sat}$ ), which is only weakly temperature-dependent.8 In the HS2 region, the electric field is sufficiently strong that electron velocity saturates, rendering it almost impervious to temperature fluctuations. Moreover, the impact of the heat source-related ballistic effect is primarily confined to the HS2 region and does not significantly influence areas farther from the heat source, consistent with observations in other numerical studies. Thus, while quasi-ballistic transport in GaN HEMTs can markedly raise the hotspot temperature, its effect on the channel electron velocity and, consequently, drain current degradation is minimal. Accordingly, the FEM simulations utilizing only  $k_{\text{film}}$  yield I-V curves that align well with experimental results, as shown in Fig. 1.

Extended simulations for HEMTs with longer gate lengths and gate-source/gate-drain spacings further support our analysis. Figures 5(a)–5(d) display the distributions of lateral electric field, temperature, electron mobility, and electron velocity in a HEMT featuring  $L_{\rm g}=1~\mu{\rm m},~L_{\rm sg}=1~\mu{\rm m},$  and  $L_{\rm gd}=3~\mu{\rm m}.$  In this long-channel design, the majority of the gated region experiences a low electric field, rendering it susceptible to temperature influences. The channel resistance in this configuration is, thus, determined by both the source access region and the low-field gate portion. Notably, Fig. 5(b) shows  $T_{\rm eq}$  shifting further into the gated region, while the high-field region at the drain-

**FIG. 5.** Distributions of (a) lateral electric field, (b) temperature, (c) electron mobility, and (d) electron velocity along the channel of the HEMT with  $L_{\rm g}=1~\mu{\rm m}$ ,  $L_{\rm sg}=1~\mu{\rm m}$ , and  $L_{\rm gd}=3~\mu{\rm m}$  for different thermal conductivity settings at  $V_g=0~{\rm V}$  and  $V_d=10~{\rm V}$ .

side gate edge remains unchanged in width ( $L_{\rm HS2}$ ). This indicates that even in extended-channel devices, the heat source-related ballistic transport still minimally affects the channel electron velocity.

Through the preceding analysis, the interplay between the two thermal metrics  $T_{\rm max}$  and  $T_{\rm eq}$ , and the non-Fourier thermal spreading process in GaN HEMTs becomes clear.  $T_{\rm max}$ , critical for device reliability, shows strong bias-dependence and is influenced by both heat source-related and cross-plane ballistic effects. In contrast,  $T_{\rm eq}$ , indicative of drain current degradation, exhibits minimal bias sensitivity and is primarily affected by the cross-plane effect. Optimizing device designs to mitigate these thermal metrics is crucial for enhancing reliability and reducing self-heating-induced performance degradation. In GaN HEMTs, thermal design optimization is significantly influenced by the heat source size. A small heat source can result in substantial thermal spreading resistance and concentrated heat flow at the GaN/ substrate interface, emphasizing the importance of interfacial thermal resistance (TBR). The distinct equivalent widths for  $T_{\text{max}}$  and  $T_{\text{eq}}$ necessitate careful consideration in device design to satisfy both metrics effectively.

In conclusion, this Letter presents a comprehensive analysis of self-heating effects in GaN HEMTs using TCAD and phonon MC simulations. It elucidates the distinct behaviors of  $T_{\rm max}$  and  $T_{\rm eq}$  in relation to non-Fourier heat spreading.  $T_{\rm max}$  is found to be highly bias-dependent and influenced by both cross-plane and heat source-related ballistic effects, particularly in the saturation regime. Conversely,  $T_{\rm eq}$  is less sensitive to bias and primarily impacted by the cross-plane effect. The insights gained from this study highlight the need for device designs that effectively address both  $T_{\rm max}$  and  $T_{\rm eq}$  offering valuable guidance for enhancing GaN HEMT designs.

The authors acknowledge the help from Professor Lan Wei and Dr. Xuesong Chen. This work was supported by the National Natural Science Foundation of China under Grant Nos. U20A20301, 52327809, and 52250273.

# AUTHOR DECLARATIONS Conflict of Interest

The authors have no conflicts to disclose.

# **Author Contributions**

Yang Shen: Conceptualization (equal); Formal analysis (equal); Investigation (equal); Methodology (equal); Software (equal); Validation (equal); Visualization (equal); Writing – original draft (equal). Bingyang Cao: Funding acquisition (equal); Project administration (equal); Supervision (equal); Writing – review & editing (equal).

## **DATA AVAILABILITY**

The data that support the findings of this study are available within the article.

# **REFERENCES**

<sup>1</sup>M. Meneghini, C. De Santi, I. Abid, M. Buffolo, M. Cioni, R. A. Khadar, L. Nela, N. Zagni, A. Chini, F. Medjdoub *et al.*, "GaN-based power devices: Physics, reliability, and perspectives," J. Appl. Phys. **130**, 181101 (2021).

- <sup>2</sup>B. Padmanabhan, D. Vasileska, and S. Goodnick, "Reliability concerns due to self-heating effects in GaN HEMTs," J. Integr. Circuits Syst. 8, 78–82 (2020).

- <sup>3</sup>S. Choi, S. Graham, S. Chowdhury, E. R. Heller, M. J. Tadjer, G. Moreno, and S. Narumanchi, "A perspective on the electro-thermal co-design of ultra-wide bandgap lateral devices," Appl. Phys. Lett. 119, 170501 (2021).

- <sup>4</sup>Y.-C. Hua, Y. Shen, Z.-L. Tang, D.-S. Tang, X. Ran, and B.-Y. Cao, Near-Junction Thermal Managements of Electronics (Elsevier, 2023), Chap. 8, pp. 355–434.

- <sup>5</sup>K. Park and C. Bayram, "Thermal resistance optimization of GaN/substrate stacks considering thermal boundary resistance and temperature-dependent thermal conductivity," Appl. Phys. Lett. 109, 151904 (2016).

- <sup>6</sup>C. Song, J. Kim, and J. Cho, "The effect of GaN epilayer thickness on the nearjunction thermal resistance of GaN-on-diamond devices," Int. J. Heat Mass Transfer 158, 119992 (2020).

- <sup>7</sup>B. Chatterjee, C. Dundar, T. E. Beechem, E. Heller, D. Kendig, H. Kim, N. Donmezer, and S. Choi, "Nanoscale electro-thermal interactions in AlGaN/GaN high electron mobility transistors," J. Appl. Phys. 127, 044502 (2020).

- <sup>8</sup>X. Chen, S. Boumaiza, and L. Wei, "Self-heating and equivalent channel temperature in short gate length GaN HEMTs," IEEE Trans. Electron Devices **66**, 3748–3755 (2019).

- <sup>9</sup>X. Chen, S. Boumaiza, and L. Wei, "Self-heating in short-channel GaN HEMTs: Maximum channel temperature and equivalent channel temperature," in 6th IEEE Electron Devices Technology & Manufacturing Conference (EDTM) (IEEE, 2022), pp. 351–353.

- <sup>10</sup>H. Bao, J. Chen, X. Gu, and B. Cao, "A review of simulation methods in micro/nanoscale heat conduction," ES Energy Environ. 1, 16–55 (2018).

- <sup>11</sup>D.-S. Tang, G.-Z. Qin, M. Hu, and B.-Y. Cao, "Thermal transport properties of GaN with biaxial strain and electron-phonon coupling," J. Appl. Phys. 127, 035102 (2020).

- <sup>12</sup>Q. Hao, H. Zhao, Y. Xiao, and M. B. Kronenfeld, "Electrothermal studies of GaN-based high electron mobility transistors with improved thermal designs," Int. J. Heat Mass Transfer 116, 496–506 (2018).

- <sup>13</sup>Y. Hu, Y. Shen, and H. Bao, "Ultra-efficient and parameter-free computation of submicron thermal transport with phonon Boltzmann transport equation," Fundam. Res. (published online).

- <sup>14</sup>J. Xu, Y. Hu, and H. Bao, "Quantitative analysis of nonequilibrium phonon transport near a nanoscale hotspot," Phys. Rev. Appl. 19, 014007 (2023).

- 15Y. Shen, H.-A. Yang, and B.-Y. Cao, "Near-junction phonon thermal spreading in GaN HEMTs: A comparative study of simulation techniques by full-band phonon Monte Carlo method," Int. J. Heat Mass Transfer 211, 124284 (2023).

- 16Y. Shen, X.-S. Chen, Y.-C. Hua, H.-L. Li, L. Wei, and B.-Y. Cao, "Bias dependence of non-Fourier heat spreading in GaN HEMTs," IEEE Trans. Electron Devices 70, 409–417 (2023).

- <sup>17</sup>X. Chen, S. Boumaiza, and L. Wei, "Modeling bias dependence of self-heating in GaN HEMTs using two heat sources," IEEE Trans. Electron Devices 67, 3082–3087 (2020).

- <sup>18</sup>W. Jatal, U. Baumann, K. Tonisch, F. Schwierz, and J. Pezoldt, "High-frequency performance of GaN high-electron mobility transistors on 3C-SiC/Si substrates with Au-free ohmic contacts," IEEE Electron Device Lett. 36, 123–125 (2015).

- <sup>19</sup>M. Singh, Y.-R. Wu, and J. Singh, "Velocity overshoot effects and scaling issues in III-V nitrides," IEEE Trans. Electron Devices 52, 311–316 (2005).

- <sup>20</sup>Q. Hao, H. Zhao, Y. Xiao, Q. Wang, and X. Wang, "Hybrid electrothermal simulation of a 3-D fin-shaped field-effect transistor based on GaN nanowires," IEEE Trans. Electron Devices 65, 921–927 (2018).

- <sup>21</sup>G. Masetti, M. Severi, and S. Solmi, "Modeling of carrier mobility against carrier concentration in arsenic-, phosphorus-, and boron-doped silicon," IEEE Trans. Electron Devices 30, 764–769 (1983).

- <sup>22</sup>C. Canali, G. Majni, R. Minder, and G. Ottaviani, "Electron and hole drift velocity measurements in silicon and their empirical relation to electric field and temperature," IEEE Trans. Electron Devices 22, 1045–1047 (1975).

- <sup>23</sup>Q. Hao, H. Zhao, and Y. Xiao, "A hybrid simulation technique for electrothermal studies of two-dimensional GaN-on-SiC high electron mobility transistors," J. Appl. Phys. 121, 204501 (2017).

- <sup>24</sup>J.-P. M. Péraud and N. G. Hadjiconstantinou, "An alternative approach to efficient simulation of micro/nanoscale phonon transport," Appl. Phys. Lett. 101, 153114 (2012).

- 25Y.-C. Hua, H.-L. Li, and B.-Y. Cao, "Thermal spreading resistance in ballistic-diffusive regime for GaN HEMTs," IEEE Trans. Electron Devices 66, 3296–3301 (2019).

<sup>&</sup>lt;sup>26</sup>Y.-C. Hua and B.-Y. Cao, "Ballistic-diffusive heat conduction in multiply-constrained nanostructures," Int. J. Therm. Sci. **101**, 126–132 (2016).

<sup>27</sup>B. Vermeersch, R. Rodriguez, A. Sibaja-Hernandez, A. Vais, S. Yadav, B. Parvais, and N. Collaert, "Thermal modelling of GaN & InP RF devices with intrinsic account for nanoscale transport effects," in *International Electron Devices Meeting (IEDM)* (IEEE, 2022).

<sup>&</sup>lt;sup>28</sup>J. Cho, Z. Li, M. Asheghi, and K. E. Goodson, "Near-junction thermal management: Thermal conduction in gallium nitride composite substrates," <u>Annu. Rev. Heat Transfer</u> 18, 7 (2015).

<sup>29</sup>C. Song, J. Kim, H. Lee, and J. Cho, "Fundamental limits for near-junction conduction cooling of high power GaN-on-diamond devices," Solid State Commun. 295, 12–15 (2019).